ARINC664 terminal IP core is a FPGA based IP complying with the new generation avionics bus standard ARINC664 specifications. The FPGA IP uses Xilinx FPGA, which provides two 10/100Mbps full duplex ARINC664 ports.

FC terminal IP core is a data communication unit module of FC terminal implemented according to FC-FS and FC-AE-ASM protocol specifications of optical fiber communication frame and signal issued by international T11 organization. It adopts Xilinx high-performance FPGA and provides 2-way redundant fiber channel interfaces with 1, 2 and 4Gbps data rates.

ARINC664 switch IP core is a FPGA based IP complying with the new generation avionics bus standard ARINC664 specification. FPGA IP uses Xilinx FPGA and provides 9-way 10/100Mbps full duplex ARINC664 ports.

The satellite mobile communication series chips developed by Hwa Create adopt SoC architecture and advanced process design, with the characteristics of low power consumption, high integration and complete functional components. The chip integrates TianTong-1 satellite mobile communication and BDS/GPS positioning to realize the integrated design of communication and navigation.

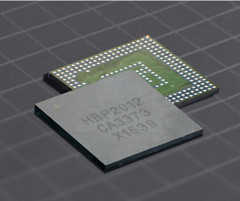

HBP2012 satellite navigation baseband chip is a high-performance SoC chip which can receive BDS, GPS, GLONASS and BDS RDSS signals simultaneously, achieving multi system multi frequency integrated positioning and short message communication, and adapt to the demand of high dynamic carrier. Through software configuration